DO NOT SCRAP IT! MODERATED NATIONAL EXCHANGE NEWSGROUP FOR SALVAGERS > Colorado

> 71V632S5PF / IDT71V632S5PF / IDT71V632 / 71V632 / pulls

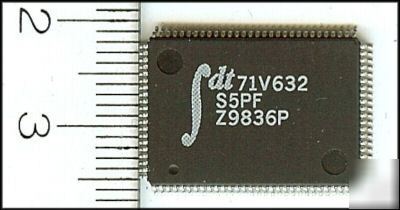

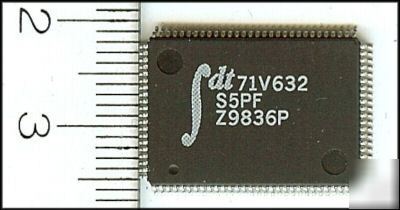

71V632S5PF / IDT71V632S5PF / IDT71V632 / 71V632 / pulls

71V632S5PF / IDT71V632S5PF / IDT71V632 / 71V632 / pulls

Now over 1,500 items in our Store!

These parts are PULLS and they might have some small amounts of solder on the leads. The leads are straight and the surface of the chips are in very good condition.

Please note: This spec sheet may cover several different parts. The spec sheet may also be from a manufacturer other than the manufacturer offered in this sale.

64K x 32 3.3V Synchronous SRAM Pipelined Outputs Burst Counter, Single Cycle Deselect IDT71V632

* Supports high system speed:

– A4 4.5ns clock access time (117 MHz)

– 5 5ns clock access time (100 MHz)

– 6 6ns clock access time (83 MHz)

– 7 7ns clock access time (66 MHz)

* Single-cycle deselect functionality (Compatible with Micron Part # MT58LC64K32D7LG-XX)

* LBO input selects interleaved or linear burst mode

* Self-timed write cycle with global write control (GW), byte write enable (BWE), and byte writes (BWx)

* Power down controlled by ZZ input

* Operates with a single 3.3V power supply (+10/-5%)

* Packaged in a JEDEC Standard 100-pin rectangular plastic thin quad flatpack (TQFP).

The IDT71V632 is a 3.3V high-speed SRAM organized as 64K x 32

with full support of the Pentiumâ„¢ and PowerPCâ„¢ processor interfaces.

The pipelined burst architecture provides cost-effective 3-1-1-1 secondary cache performance for processors up to 117MHz.

The IDT71V632 SRAM contains write, data, address, and control registers. Internal logic allows the SRAM to generate a self-timed write based upon a decision which can be left until the extreme end of the write cycle.

The burst mode feature offers the highest level of performance to the system designer, as the IDT71V632 can provide four cycles of data for a single address presented to the SRAM. An internal burst address counter accepts the first cycle address from the processor, initiating the access sequence. The first cycle of output data will be pipelined for one cycle before it is available on the next rising clock edge. If burst mode operation is selected (

ADV=LOW), the subsequent three cycles of output data will be available to the user on the next three rising clock edges. The order of these three addresses will be defined by the internal burst counter and the LBO input pin.

The IDT71V632 SRAM utilizes IDT's high-performance, high-volume 3.3V CMOS process, and is packaged in a JEDEC Standard 14mm x 20mm 100-pin thin plastic quad flatpack (TQFP) for optimum board density in both desktop and notebook applications.

Temporary Email: j.mcpherson@dontscrapit.com (Jewell Mcpherson)